How to reduce the cost of tape-out?

The chip industry is no stranger to the term "tape-out."

The so-called tape-out refers to the process of manufacturing chips through a series of production steps, much like an assembly line. In simple terms, it involves a chip company handing over a well-designed plan to a wafer fabrication plant. The plant then produces a small number of samples to test whether the designed chips are functional. The results of these tests determine whether the design needs to be optimized or if mass production should commence. Therefore, to test the success of an integrated circuit design, a tape-out is essential, which is also a significant reason why chip design companies generally require substantial initial investment.

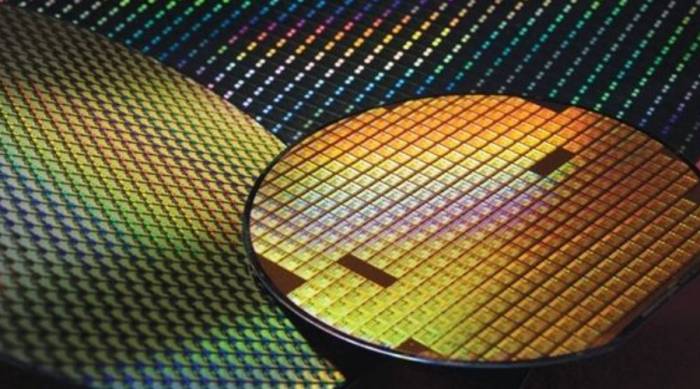

From design to mass production, the tape-out is a crucial step for a chip. After a chip is fully designed, it needs to be etched on a wafer according to the blueprint. The choice of manufacturing process, the size of the wafer, and the complexity of the chip all affect the success rate and cost of the tape-out. Moreover, many chips do not succeed on the first tape-out attempt and often require multiple tape-outs to achieve a more desirable outcome.

However, tape-out is an extremely costly endeavor. Major chip manufacturers have calculated that for a 14nm process chip, a single tape-out costs around 3 million US dollars, for a 7nm process chip, it costs 30 million US dollars, and for a 5nm process chip, it reaches a staggering 47.25 million US dollars. It is evident that tape-out is a huge expense for chip design companies, especially for small and medium-sized enterprises in the industry, where the actual tape-out cost is much higher than that of large manufacturers, exacerbating their already tight financial situation.

Advertisement

Why is tape-out so expensive?

The high cost of chip tape-out can be attributed to the manufacturing principles of chips. Chip manufacturing involves placing hundreds of millions of transistors in a very small chip, with manufacturing processes reaching the nanometer level, which can only be accomplished through photolithography. Photolithography is the process of using light to etch the desired patterns. This process requires the use of photomasks (also known as reticles or masks), which are used to engrave the designed circuit diagram, allowing light to pass through and etch the pattern onto the wafer.

The high cost of tape-out is partly due to the need for verification of many processes at the beginning. From a circuit diagram to a chip, each production step must be tested for feasibility, and the circuit must be tested for the required performance and functionality. The tape-out process for a chip lasts at least three months (including material preparation, photolithography, doping, electroplating, and packaging testing), and generally involves more than 1,000 production steps, making it the most important and costly part of chip manufacturing.

If the tape-out is successful, mass production of chips can be carried out accordingly; otherwise, the reasons must be identified and corresponding optimization designs must be made.

Among the factors contributing to the high cost of chip tape-out, the main expenses are the photomasks and wafers, both of which are consumables and are not cheap. The photomasks are the most expensive, with a set of mid-range process technology photomasks costing around 500,000 US dollars, and the price of a single wafer is also in the thousands of US dollars.Which is more expensive, the photomask or the wafer?

The photomask is a pattern transfer tool or master in the microelectronics manufacturing process, functioning similarly to the "film" in a traditional camera. Based on the customer's required patterns, micrometer and nanometer-level fine patterns are engraved on the photomask substrate through photolithography plate-making processes. It serves as a carrier for graphic design and process technology content.

The process of transferring the patterns from the photomask to the wafer is somewhat similar to the workflow of a printing press. Imagine the lithography machine as a printing press, the wafer as the printing paper, and the photomask as the printing plate. The process of printing the patterns of the banknote master onto the paper is akin to the lithography machine imprinting the chip patterns from the photomask onto the wafer.

The price of the photomask mainly depends on the "process node" chosen for the chip. The higher the process node, the more expensive the wafer price becomes. This is because the more advanced the process node, the more layers of photomasks are required. It is understood that about 60 photomasks are needed for the 14nm process, and 7nm may require 80 or even hundreds of photomasks.

The increase in the number of photomask layers is not only due to the high price of the photomasks but also because each additional "photomask" requires an additional "lithography," an additional application of "photoresist," an additional "exposure," followed by another "development"... The overall cost of the entire process is significantly increased.

According to data from IBS, the photomask cost used in the 16/14nm process is around 5 million US dollars, and it quickly rises to 15 million US dollars when the process reaches 7nm.

The overall cost of the photomask includes the cost of raw materials such as quartz and photoresist, the use of equipment such as Mask Writer and Inspection, as well as the generation of photomask-related data, including software licensing for OPC, MDP, server usage, and labor development costs, etc. For a chip, with dozens of layers of photomasks, so many steps are required, and equipment, software, and personnel are indispensable, making the cost naturally expensive.

According to insiders, the photomask cost for a wafer foundry's 40nm tape-out is about 600,000 to 900,000 US dollars; after entering mass production, each wafer may be around 3,000 to 4,000 US dollars. Therefore, when producing 5-25 pieces for product verification in the early stage, the mask cost is the main factor; if mass production is large, the mask cost is very small after being averaged to each wafer, and then it is the wafer that dominates the cost. To be precise, it should be that the cost per chip is cheaper, not the total tape-out cost.

How to reduce tape-out costs?

Under the influence of the above factors, the cost of chip tape-out has become a problem for design companies. So, in the face of high tape-out prices, is there any way to reduce costs?MPW (Multi Project Wafer) is a type of fabrication method that can help design companies reduce costs. MPW refers to the sharing of a single wafer by multiple projects, where a single manufacturing process can undertake the production tasks of multiple IC designs. Multiple integrated circuit designs using the same process are placed on the same wafer for fabrication. After the manufacturing is completed, each design can receive dozens of chip samples, which is sufficient for experiments and tests during the prototype design phase.

In layman's terms, several companies or institutions jointly purchase a set of masks, and then several types of chips will exist on the same wafer produced. After the wafer is cut, each company takes their respective chips "home". The manufacturing cost of this time is shared by all participating MPW projects according to the chip area, greatly reducing the risk of product development.

MPW has a certain process, usually organized by wafer foundries or third-party service organizations. The MPW time points for various processes within a year are pre-set, usually the more advanced the process, the higher the frequency of MPW arranged. Wafer foundries will pre-divide the wafer into multiple areas and quote prices in advance, and each company will book one or more areas according to their own situation.

For participants, there is a certain pressure on the progress of design and development. However, compared to this, the benefits brought by MPW are obvious. Using multi-project wafers can reduce the production cost of chips, provide practice opportunities for designers, and promote the transformation of chip design results. It has a considerable promoting effect on the training of IC design talents, the development of small and medium-sized design companies, and the development and research of new products.

In comparison, the advantage of sharing a mask is cost-saving, but it may have to wait for the time nodes of the foundry, requiring more time. For those companies that are not short of money or are in a hurry, they can of course use a set of masks (Full-Mask, full mask) by themselves. All masks in the manufacturing process serve their own design, usually used in the mass production stage after the design is finalized. Once the machine starts, there is a lot of money to be made.

Therefore, improving the success rate of a single tape-out is also an important factor in reducing the cost of tape-out.

In fact, for most small and medium-sized enterprises, in addition to the price, there are still many challenges in the tape-out or mass production process, including capacity, delivery time, etc.:

1. Lack of understanding of the foundry system, lack of experience in process selection and dealing with foundries;

2. The entry threshold of mainstream foundries is high, and it is difficult for emerging players to apply for the expected process or support, and the communication cost is high;

3. Lack of systematic supply chain management ability, especially in the mass production capacity ramp-up stage, being too optimistic about capacity, delivery time, and quality.In situations of production capacity shortage, the lack of a backup mechanism can lead to panic ordering or ordering after receiving orders, which results in production capacity not keeping up with market demand. In addition, changes in delivery times and fluctuations in production capacity will greatly increase the communication costs between start-up companies and wafer foundries, reducing efficiency.

Moore Elite, safeguarding customer chip tape-out

In response, small and medium-sized chip design companies can seek cooperation with third-party tape-out service platforms that have resources and experience to solve the supply chain problems they encounter.

With Moore Elite's tape-out services, a complete process platform can be provided, connecting with dozens of mainstream wafer foundries, offering tape-out services at different process nodes including MPW, Full-mask, and mass production, which can significantly reduce customers' business and communication costs.

On the other hand, with its own professional tape-out FAE team, it not only provides efficient support and management for long-tail customers for cooperative wafer foundries but also helps small and medium-sized companies' products to get support quickly, assists customers in choosing the best process, and ensures the security of customer data.

In terms of production capacity, Moore Elite uses its know-how to assist small and medium-sized customers in securing production capacity (including large orders, order volume trends, early queuing, and timely tracking of production capacity dynamics), helping customers reduce costs and shorten the chip development cycle.

Since upgrading its business model in 2018, Moore Elite has invested in building its own 20,000 square meter packaging and testing capacity, with Hefei Quick Packaging Engineering Center, Chongqing Quick Packaging Engineering Center, and Wuxi SiP Packaging and Testing Center successively put into operation. Our service capabilities focus on SiP packaging, Flip-chip packaging, rapid engineering packaging, and mass production testing services based on self-owned ATE equipment. With its own packaging and testing delivery capabilities, it also provides customers with a fast track from prototype to mass production.

About Moore Elite

Moore Elite is committed to "making chip development easy in China" by providing an efficient "one-stop chip design and supply chain platform" that combines its own packaging and testing factory and equipment's rapid response capabilities. It offers a one-stop delivery solution from chip development to mass production for chip and terminal companies with diverse and customized chip needs.Moore Elite provides customers with platform-based, customized, and productized chip design services, IT/CAD design platform services, wafer fabrication services, packaging services, testing services, product engineering and mass production management services, and semiconductor education and training services. These services help customers to accelerate and differentiate the mass production of their products, improve the efficiency of R&D and operations, and reduce the risks of pitfalls and failures.

Moore Elite has established its R&D and operational headquarters in Shanghai, introduced chip automatic test equipment (ATE) from leading international IDMs, set up two overseas R&D centers in Dallas, USA, and Nice, France, and built a 20,000 square meter packaging and testing factory in Wuxi, Chongqing, Hefei, and other places. The core equipment investment exceeds 300 million yuan, and the supply chain partners cover mainstream wafer fabs and packaging and testing factories worldwide.

Leave A Comment