Review and outlook of CIS manufacturing process.

Abstract: CMOS image sensors are experiencing tremendous growth due to their ability to be integrated into smartphones with high image quality. One of the main contributions to the development of image sensors is the innovation in their manufacturing processes. This paper provides a detailed review of the different manufacturing processes of CMOS image sensors and their impact on the image quality of smartphones. The discussion includes the manufacturing of CMOS image sensors using technologies such as Through-Silicon Vias (TSVs) and Cu-Cu hybrid bonding, along with experimental results. The dual-layer structure of photodiodes and pixel transistors is integrated sequentially in 3D, with wafers being bonded one after another during the manufacturing process. The paper presents the electrical characteristics and reliability test results for the first two manufacturing processes and discusses the improvements in pixel performance (such as conversion gain, quantum efficiency, full well capacity, and dynamic range) due to the two-layer structure.

1. Introduction

Photography is one of the many features that have driven significant growth in the smartphone industry. In recent years, there has been a considerable improvement in the image quality of camera phones and smartphones, leading to a decline in the market share of digital cameras, as shown in Figure 1. This is due to the ability to miniaturize image sensors and embed them into smartphones, achieving image quality comparable to that of digital cameras.

Cameras have a long history dating back to the 19th century. The first digital camera prototype was built at Bell Labs in 1973, based on an image sensor known as the Charge-Coupled Device (CCD). Subsequently, the first commercial digital camera—the MOS sensor-based Cromemco Cyclops—emerged in 1975. This camera had no built-in permanent memory and had to be connected to a computer to view images. Figure 2 shows a 32x32 pixel image captured by the Cyclops.

Advertisement

Most smartphone cameras today are based on Complementary Metal-Oxide-Semiconductor (CMOS) Image Sensor (CIS) technology. Since its invention at the Jet Propulsion Laboratory in 1993, the industry has started adopting CIS technology in smartphone cameras. Since then, the image quality of smartphone pictures has greatly improved due to the development of CIS manufacturing processes. This is evident from Figure 3, which shows an image captured by an iPhone (with CIS) over a decade ago. The improvement in image quality is marked by the yellow frame in the images captured at minimum brightness by the iPhone 4 (2010) and iPhone 3GS (2009). The latest advancements in CIS can be seen in the photos taken by the iPhone 14 (2022), which was captured under the dark sky, as shown in Figure 4. It is not difficult to see the growth of CIS and its contribution to the smartphone industry from the comparison of images in Figures 3 and 4.

A. Working Principle of CIS

Image sensors are semiconductor devices that detect photons and convert them into electrical signals, which are then processed to form meaningful images. Photodiodes capture photons and convert them into electrons, which are then converted into voltage. An Analog-to-Digital Converter (ADC) is used to convert this analog information into digital information, which is further processed to obtain the final image. Although CIS is a widely used image sensing technology today, its basic working principle originates from its predecessor, the Charge-Coupled Device (CCD).The comparison of the working principles of CCD and CIS is shown in Figure 5. Both CCD and CIS consist of an array of pixels. Each pixel is composed of photodiodes and electrodes in CCD, and photodiodes and transistors in CIS. In CCD, when photons strike the photodiodes, they are converted into electrons, which are then transferred from one pixel to another and finally to a register, where they are converted into voltage and amplified. In contrast to CCD, in CIS pixels, voltage information is obtained within the pixel itself, and subsequently, the voltage is read simultaneously using vertical or horizontal strips from all pixels. Some CIS have an ADC on the chip itself, and the sensor's output has already been digitized. Due to the faster information readout speed, minimal information loss, and low power consumption in CIS, they have replaced CCD over the past decade.

B. Evolution of CIS

Since its invention in 1993, the CMOS image sensors available on the market today have gone through several generations of development. Traditional CIS is front-illuminated, with microlenses and color filters on top, followed by metal wiring for interconnection and photodiodes located at the bottom of the architecture. As light enters the image sensor through the metal layer, some light signals are reflected and lost during the transmission process, even before reaching the photodiodes. Clearly, this arrangement affects the performance of front-illuminated sensors, and this issue was resolved when Sony proposed moving the photodiodes to the top of the architecture next to the color filters. This structure is called a back-illuminated (BI) CMOS image sensor, which greatly improved the sensor's performance, marking the beginning of a new era for CMOS image sensors. The comparison between front-illuminated and back-illuminated CMOS image sensors is shown in Figure 6.

Following the back-illuminated sensors, scholars proposed the idea of stacking pixels and logic electronics to reduce the sensor's size in the X and Y directions. Figure 7 shows the three-dimensional view of a traditional BI-CIS (left), where the sensor's pixels and logic circuits share the same substrate, and a stacked sensor (right), where the pixel part containing the photodiodes is placed on top, and the logic circuits are moved to the bottom of the architecture on the supporting substrate. This is called a stacked back-illuminated CMOS image sensor, proposed by Sony in 2012.

This article introduces various research works carried out in the industry and demonstrates some improvements in stacked back-illuminated CMOS image sensors (BI-CIS). The research work focuses on exploring various manufacturing processes for stacked sensors and improving different performance indicators of photodiodes. These advancements are crucial for the development of CMOS image sensors, as they, in turn, contribute to the smartphone industry.

2. Stacked BI-CIS using Through-Silicon Vias (Researchers: H. Tsugawa et al., 2017)

Rolling shutter distortion is a common phenomenon in smartphones and professional digital cameras. This image distortion occurs when the object of interest to be captured moves at a speed greater than the sensor's speed, and the bottom of the frame is captured later than the top of the frame. This lag causes image distortion, and the mechanical shutter in digital cameras overcomes this issue by only exposing the sensor to a specific time frame that the sensor can handle. However, mechanical shutters cannot be used in smartphones to reduce image distortion. The motivation behind the research discussed in this article is to explore ways to reduce image distortion in smartphone CIS.Studies have shown that image distortion in CMOS sensors is caused by the low readout speed at the output interface of the sensor structure. As shown in Figure 8, in traditional stacked CIS, image information from the pixel layer reaches the logic circuit through the DRAM layer and leaves the output interface (I/F) in a serial manner. Even if the pixel part can capture the entire image, the interface can only read out the information serially. Compared with the pixel side, this leads to a delay in readout speed at the I/F, resulting in distortion. To eliminate distortion, adding a temporary memory to store pixel information seems to be a feasible solution. However, this means that the pixel size is increasing, which affects the image resolution.

By changing the data flow in the image sensor architecture rather than the pixels, the image distortion at the I/F can be improved. A 1Gbit DRAM memory layer was added between the logic layer and the I/F layer, and Figure 9 shows a 3-layer pixel/DRAM/logic configuration. The output of the pixel reaches the logic layer through DRAM, and then the data from the logic layer is temporarily stored in the DRAM layer until the I/F is ready to read the information. It should be noted that the readout speed on the pixel side is increased to 120fps, while the readout speed at the I/F remains at 30fps, which is the same as without DRAM. Adding a DRAM layer at the pixel output and a readout speed of 120fps greatly reduces the rolling shutter distortion effect in the final image.

A. Structure of Stacked BI-CIS Using Through-Silicon Vias (TSVs)

The 3-layer stacked CIS structure shown in Figure 9 uses two layers of stacked TSVs, with a 90nm CMOS process for the pixels, a 30nm process for the DRAM, and a 40nm process for the logic layer. The intermediate DRAM and logic layers are connected by the lower TSV stack, and the pixel substrate and lower TSV stack are connected by the upper TSV stack.

B. Through-Silicon Via (TSV) Process Flow

The process flow for the 3-layer stacked CIS is shown in Figure 10. The manufacturing process begins with parallel processing of the wafers, each connected to its respective substrate. The DRAM is flipped and bonded to the surface of the logic substrate. After bonding, the DRAM substrate is thinned to about 3μm. Then, the lower TSV is formed and the metal wiring connecting the two substrates is made. Subsequently, the pixel substrate is flipped and bonded to the already stacked DRAM/logic substrate, and then the upper TSV is made to connect the pixel substrate to the rest of the stack.

C. Experimental Verification Using Test ModulesResearchers conducted various tests to analyze the electrical and reliability characteristics of TSV interconnects in a three-layer stacked CMOS process. The researchers fabricated a 300mm wafer with 9,000 TSV chains, which served as the test module. The TSV chains extend from the top of the pixel layer to DRAM and then to the logic substrate. Figure 11 shows the cumulative probability of the initial resistance measured for the 9,000 TSV chains. Measuring resistance is crucial for any type of interconnect because they are parasitic and cause propagation delay for signals passing through them. Based on the results, the researchers concluded that the initial resistance was very small, and the variation in resistance values between different TSV chains was minimal. Additionally, stress migration testing was performed on 1,260 TSV units using an annealing process. During the annealing process, the test module was exposed to 175°C for 1,000 hours, and the curve chart in Figure 12 shows that the resistance shift of the 1,260 units was less than 2%. The change in resistance was calculated before and after annealing. Furthermore, the leakage current between TSVs and their substrates was measured by applying 1V between the TSV and DRAM substrate. When using DRAM, leakage current is a critical factor, as high leakage current can lead to low retention time in DRAM. From Figure 13, the researchers found that the leakage current was very low, with minimal variation between different units.

Dielectrics can be damaged and form conductive paths when exposed to high electric fields for extended periods. Therefore, a time-dependent dielectric breakdown (TDDB) test was conducted on the test module by applying 180V between DRAM and TSV for an extended period. After 10,000 seconds, the researchers concluded that the breakdown was significantly reduced, indicating that the insulation performance between the DRAM substrate and TSV was sufficient, as shown in Figure 14, which presents the experimental test conducted on the 300mm test module.

D. Development of a Three-layer Pixel/DRAM/Logic Chip

After the test module was verified, the researchers fabricated a three-layer pixel/DRAM/logic stacked chip, with a cross-sectional view shown in Figure 15. In the figure, the pixels are displayed in the entire cross-section, and the periphery shows the stacked TSV chains that form the connection between the pixel DRAM and the DRAM logic substrate. The upper TSV has a diameter of 2.5µm, connecting the pixels and DRAM substrate, with approximately 15,000 TSVs in the stacked chip. The lower TSV has a diameter of about 3.5µm, with 20,000 connecting the DRAM and logic substrate. The TSV pitch, measured from the center of one TSV to another, is 6.5µm.

Despite the addition of a third layer of DRAM in the pixel/logic stack, the researchers achieved the same thickness as a two-layer chip without DRAM. As part of the bonding process, the substrate is typically thinned, and the final thickness of the DRAM substrate after thinning is 3µm. The fabricated pixel/DRAM/logic stacked BI-CMOS chip has a thickness of 130µm, with 19.3 million pixels, pixel size of 1.22µm x 1.22µm, and a transfer rate of 30fps at the output interface.

3. Stacked BI CIS using Cu-Cu hybrid bonding (Researchers: Y. Kagawa et al., 2018)In this study, researchers have prepared stacked BI-CIS using the Cu-Cu hybrid bonding technique. Through-Silicon Vias (TSVs) provide hybrid electrical connections between the substrates, with the substrates electrically bonded through Cu-Cu metal connections, and simultaneously physically bonded through interlayer dielectrics (ILD). Compared with Cu-Cu hybrid bonding, TSVs have almost no drawbacks:

TSVs require a special manufacturing equipment known as a deep silicon etcher.

The fabrication of TSVs necessitates a keep-out zone (KOZ) around them, which is a gap area that must be free of any circuits. This limits the area available for circuit designers to use in circuit design.

TSVs only provide electrical connections between the substrates.

A comparison between TSVs and Cu-Cu bonding is shown in Figure 16. It is worth noting that, compared with TSVs, the Cu-Cu hybrid bonding technique requires less space and a simplified manufacturing process, making it an ideal choice. They also provide greater design flexibility for circuit designers.

A. Process flow of Cu-Cu hybrid bonding

The Cu-Cu bonding process begins with the preparation of the wafer. Figure 17(a) shows the formation of a thick dielectric layer on silicon using Chemical Vapor Deposition (CVD). CVD is a process where solid materials are deposited in the gas phase to achieve uniform thickness across the entire surface. Subsequently, trenches and vias are made as part of the Back-End-of-Line (BEOL). Copper seed layers are formed in the trenches using Physical Vapor Deposition (PVD). After PVD, trenches are filled with copper using Electrochemical Deposition (ECD). Excess copper is removed, and a very low dielectric roughness is achieved through Chemical Mechanical Polishing (CMP). During the CMP process, it is expected that the copper will recess to a certain extent. As shown in Figure 17(b), plasma-activated wafers are bonded face-to-face, and the dielectrics bond instantaneously. After CMP, annealing is performed at temperatures between 150°C and 300°C, so the metal will expand to fill the gaps between them. The aforementioned steps confirm that Cu-Cu hybrid bonding provides both physical and electrical connections due to the bonding of the dielectrics and metals between the substrates.

CMP plays a crucial role in achieving dielectric roughness and metal recessing. In the standard Cu-Cu bonding process, copper pads are recessed. This study employed a controllable CMP process, intentionally making the copper pads protrude, and controlling their bonding accuracy.B. Experimental Verification Using Test Modules

Similar to the research in the previous section, the electrical and reliability testing of Cu-Cu bonding was conducted on a 300mm test wafer. The 300mm wafer has 3 million Cu-Cu connections manufactured at a 4µm pitch. In addition to measuring the resistance of the copper interconnections and the contact spacing, the wafer was also subjected to TDDB testing to measure chip life. Figures 18 and 19 show the resistance and contact spacing measurements of the test module, respectively. The resistance measured before and after exposing the test wafer to 175°C for 1000 hours indicates that there was no significant change in resistance values after the high-temperature annealing process. A contact spacing of 4µm was achieved for the 3 million Cu-Cu connections in the test wafer. Figure 19 shows that, compared to previous studies, this study has been proven to have the smallest contact spacing.

C. Fabrication of Stacked BI-CIS with Cu-Cu Hybrid Bonding

The researchers then fabricated stacked BI-CIS using Cu-Cu hybrid bonding technology. In the standard Cu-Cu bonding process, the copper pads are recessed in the CMP process, and the metal expands and connects during the annealing process, but there is a problem of bonding voids at the interface. Therefore, in this study, a controllable CMP process was introduced to ensure fine electrical connections between the substrate copper pads. In this specialized process, the copper pads are intentionally protruded, so the formed substrate-to-substrate metal connections are robust, with no bonding voids. Figure 20 depicts the cross-section of the stacked BI-CMOS, from which it is evident that the substrates are bonded seamlessly at the bonding interface.

In the Cu-Cu hybrid bonding-based stacked BI-CMOS chip, a low contact spacing of 4µm was achieved, which played an important role in manufacturing small image sensor chips with enhanced design flexibility. The fabricated chip has a resolution of 22.5 megapixels, with a pixel size of 1µm x 1µm.

4. Stacked Bi-CIS with Double Layers (Researchers K. Zaitsu et al., 2022)

For decades, various industries have been committed to achieving optimal performance of image sensors while striving to reduce chip size. In studies such as the ones mentioned earlier, the photodiodes (PD) and pixel transistors share the same layer. As a result, the design area available to enhance either of their performances is limited. Researchers have made efforts to increase the density of CMOS image sensors for better performance. In recent studies, some researchers have proposed methods to miniaturize pixels, perform deep PD, and increase their fill factor. Despite this, the capacity of the photodiode has not improved due to the ion implantation process absorbing most photons. Another method to increase the volume of the PD requires long wiring to connect the sensing nodes, which leads to a reduction in conversion gain.

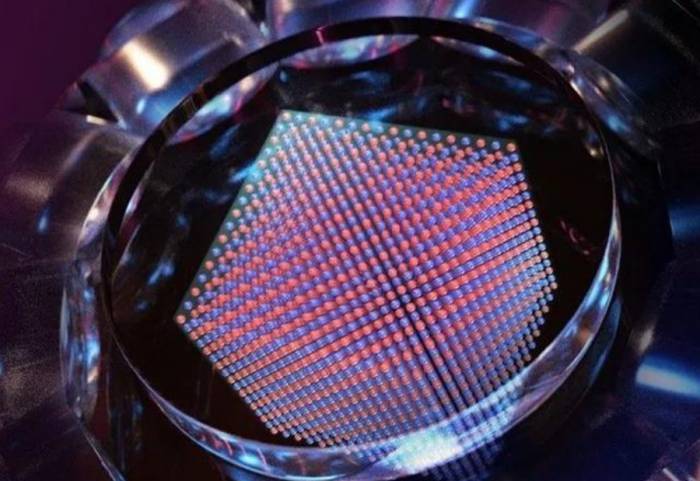

A. Structure of Double-layer Photodiode/Pixel TransistorA research work introduces a dual-layer stacked back-illuminated CMOS image sensor constructed using a three-dimensional sequential manufacturing process. The two-layer configuration of the photodiode/pixel transistor is shown in Figure 21, where the photodiodes and pixel transistors are independently designed in two different layers, creating opportunities for their optimized performance.

The dual-layer stacked CIS architecture can be better explained using the cross-section shown in Figure 22. The top layer has photodiodes and transfer gates, and the second layer has amplifiers, select gate transistors, reset gate transistors, and deep contacts connecting the first and second layers. The photodiodes are isolated from each other by a process known as Full Trench Isolation (FTI).

B. Design Optimization

In the sequential manufacturing process, few optimization efforts have improved the performance parameters of the CMOS image sensor, such as Conversion Gain (CG), Quantum Efficiency (QE), and Full Well Capacity (FWC).

(1) Conversion Gain: The pixel conversion gain (CG) is the voltage difference that the AMP (amplifier transistor) provides from the electronic charge output of the photodiode to the floating diffusion (FD) node, as shown in Figure 23. The floating diffusion is the sensing node capacitance at the RST and AMP (amplifier transistor) gates. As part of the FTI process, a large number of deep contacts are required to connect each photodiode to its pixel transistor, which increases the FD capacitance. The increase in capacitance reduces the conversion gain. Therefore, to minimize FD, the deep contact groups are connected together to form a junction called sub-partial connection, as shown in Figure 22. Sub-partial connection reduces the floating diffusion, which in turn enhances the conversion gain.

Figure 23 Conversion Gain and Quantum Efficiency

(2) Full Well Capacity: According to a research article, the full well capacity (FWC) is defined as the amount of charge that can be stored in a pixel before saturation. Figure 24 shows the full well capacity for different pixel sizes, which means that a higher FWC can be obtained with more photodiode area. In CIS, using dual photodiodes (PD) is a common process. Traditionally, boron dopants are used to isolate dual PD, which occupies the volume of the photodiode, thus reducing FWC. In the dual-layer structure, partial FTI with reduced boron injection is used to isolate PD.Translate the following passage into English:

(3) Quantum Efficiency: As stated in previous studies, quantum efficiency (QE) is a measure of the effectiveness of imaging devices in converting incident photons into electrons. This is illustrated in Figure 23 and is typically expressed as a percentage. In other words, QE represents the number of photons converted into electrons by the photodiode. In the traditional FTI process, the trenches are usually filled with polysilicon, which absorbs some of the light and reduces QE. Therefore, the authors adopted silicon oxide as the embedding material. Silicon oxide prevents light from being absorbed in the trenches, resulting in an increased quantum efficiency.

In summary, the use of partial FTI process with silicon oxide filling in a double-layer architecture is beneficial for both QE and FWC.

C. 3D Sequential Integration Process Flow

The 3D sequential integration process is achieved by building the wafer layer by layer. The challenge of subsequent integration is to manufacture the top layer without damaging the bottom substrate due to the high temperatures applied during the process. Traditional parallel processing chip manufacturing includes front-end-of-line (FEOL) and back-end-of-line (BEOL) manufacturing steps. FEOL is the first part of the manufacturing process, where individual components such as transistors, resistors, and capacitors are built, and the interconnection between layers is completed in the last step of BEOL. In the sequential process, deep contacts from the photodiode and pixel transistor layer are connected through metal interconnections, which occur between the top and bottom layers.

3D continuous integration is shown in Figure 25. Unlike parallel processing wafers, in sequential processing, the devices do not need to be combined in a predetermined pattern. Instead, the top layer devices are processed on top of the bottom layer devices. As shown in Figure 25, the first step is to form the top layer devices, which is completed by forming the active layer on the patterned wafer. This is the top FEOL, followed by etching the interconnections between the two layers and filling them with metal to establish contact between the layers.

In the study, the photodiode and transfer gate are the bottom layer devices, and the pixel transistor is the top layer device. To connect the photodiode and pixel transistor, deep contacts from these two layers are connected through metal interconnections. During the annealing process, there is a high likelihood that the photodiode and transfer gate will be affected during the formation of the top layer. Therefore, the researchers selected a suitable dielectric film to provide thermal stability during the top layer manufacturing process.

D. Fabrication and Optimization Results of Double-Layer CIS

The researchers used the sequential integration process to fabricate a double-layer photodiode/pixel CIS and measured the performance parameters of the image sensor. The cross-section of the double-layer CIS is shown in Figure 26, showing the positions of the transfer gate, pixel transistor, photodiode, and deep contact. The fabricated device has a photodiode with a size of 1μm x 1μm. Due to the partial FTI increasing the PD volume, the authors achieved a high FWC of 12,000 e- compared to previous studies, which can be seen in Figure 27.As previously mentioned, QE has been improved by combining partial FTI and using silicon oxide as the trench filling material. The QE increased by 19% at a wavelength of 530nm, as shown in Figure 28. Compared to silicon oxide, polysilicon absorbs more light, which is demonstrated by the cross-sectional simulation of the FTI in Figure 29, and this is not conducive to QE.

As shown in Figure 30, the conversion gain increased by 28% and the random noise was reduced by 14% compared to the sub-partial connection without deep contacts. The sub-partial connection reduces the number of deep contacts and, consequently, the floating diffusion capacitance.

5. Conclusion

The market share of CMOS image sensors in 2022 was $19.28 billion, and it is expected to reach $38.78 billion by 2030. This is mainly due to the increasing demand from smartphones, digital cameras, and various new applications, and the ability of CMOS image sensors to meet these demands. The design requirements of various devices range from better image resolution, reduced image distortion to improved gain, while achieving a smaller chip size. This paper reviews the relevant research papers chronologically, and it is clear that the manufacturing process has played an important role in the transformation of image sensor architecture and its performance.

Back-illuminated and stacked layers are the main concepts that mark the beginning of the use of CMOS image sensors in smartphones. Stacked layers help to reduce chip size, while back-illuminated improves sensor performance. The manufacturing process of adding DRAM layers based on TSV has played an important role in reducing rolling shutter distortion and improving image quality. The readout speed on the pixel side has been increased to 120 frames per second, while maintaining the same readout speed, with an output of 30 frames per second, ensuring that consumers do not see any delay. Later, the Cu-Cu hybrid bonding technology was adopted, which has been proven to be an effective and convenient substrate bonding method, while successfully providing design flexibility and reducing chip size. This has made it possible to integrate multiple cameras in smartphones.

Finally, we explored the double-layer architecture, where pixels and photodiodes are placed in two different layers using a 3D sequential integration process. In addition to adopting this process, other manufacturing technologies such as sub-partial connections and partial FTI with silicon oxide have been used, and a high FWC of 12000 e- has been achieved through these technologies. Compared with previous technologies, the double-layer architecture conversion gain has increased by 28%, and the quantum efficiency has increased by 19%. Moreover, when different shades of bright and dark areas in the image are captured, the double-layer architecture increases the dynamic range of the photodiode, thereby improving image quality.

It is expected that CMOS image sensors will continue to appear on smartphones and may replace digital cameras in the distant future.

Leave A Comment